Spintronic Memory (MRAM)

The MRAM design targets the 1Tr-1MTJ STT-MRAM, the 2Tr-2MTJ Twin STT-MRAM, the 4Tr-2MTJ differential STT-MRAM, and the SOT-MRAM.

The 1Tr-1MTJ STT-MRAM is the technology for large-capacity MRAM with the smallest cell size. The 2Tr-2MTJ Twin STT-MRAM and the 4T-2MTJ differential STT-MRAM are technologies for LLC (Last Level Cache) and L2 caches with excellent high-speed operation. SOT-MRAM is a next-generation MRAM technology that has not yet begun mass production, but it is an attractive technology with ultra-high-speed performance that achieves 0.3 nsec, and is a technology for HPC, including L1 cache.

For memory, we perform everything from analog and physical design such as cell design and S/A to logical design, verification, and physical design such as MRAM peripheral circuits and power management architecture for the entire chip.

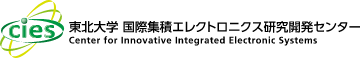

SOT-MRAM

(2020 IEEE Symposium on VLSI Circuit)

Spintronics Logic (AI Processor, MCU etc.)

Logic achieves a significant reduction in power consumption (1/100) by replacing e-Flash, which is an existing embedded non-volatile memory, with MRAM, and by replacing SRAM, which is an embedded volatile memory, with MRAM, and by reducing the cell size, it achieves a low price by reducing the chip size of logic.

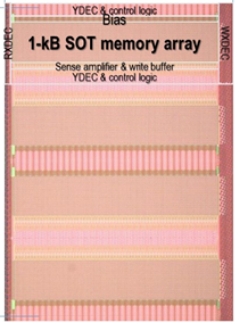

In the future, we aim to introduce spintronics technology not only in the logic embedded memory section but also in the Arithmetic Logic Unit by introducing non-volatile latch circuit and non-volatile flip-flop circuit using spintronics technology. As a result, we have succeeded in developing microcontrollers, FPGAs, and neural network-type AI processors for image recognition.

In terms of logic, we perform a series of operations from embedded MRAM macro design to power management (power gating, clock gating, etc.) architecture of various logic chips, as well as logical design, verification, and physical design.

FPGA MPU

(IEEE ISSCC 2019)