スピントロニクスメモリ(MRAM)

MRAMの設計では、1Tr-1MTJ型STT-MRAM、2Tr-2MTJ型Twin STT-MRAM、4Tr-2MTJ型差動STT-MRAM、SOT-MRAMを対象としています。

1Tr-1MTJ型STT-MRAMは、最もセルサイズが小さく、大容量MRAM向けの技術です。2Tr-2MTJ型Twin STT-MRAMと、4T-2MTJ型差動STT-MRAMは、高速動作性に優れたLLC(ラストレベルキャッシュ)やL2キャッシュに向けた技術です。SOTーMRAMは、まだ量産が始まっていない次世代MRAM技術ですが、0.3nsecを達成する超高速性能が魅力の技術で、L1キャッシュ含めHPC向けの技術です。

メモリについては、セル設計やS/A等のアナログ・物理設計から、MRAMの周辺回路やチップ全体のパワーマネージメントアーキテクチャ等の論理設計・検証・物理設計までの業務を行っています。

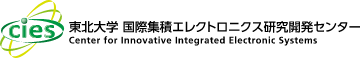

SOT-MRAM

(2020 IEEE Symposium on VLSI Circuit)

スピントロニクスロジック

(AI プロセッサー、マイコンなど)

ロジックは、既存の混載不揮発性メモリであるe-FlashをMRAMで置き換えたり、混載揮発メモリであるSRAMをMRAMで置き換えることで、消費電力を大幅に削減(1/100)を達成したり、セルサイズの縮小効果により、ロジックのチップサイズの削減による低価格化を実現します。

また、将来的には、スピントロニクス技術を用いた不揮発性ラッチ回路や不揮発性不リップフロップ回路を導入することで、ロジックの混載メモリ部のみならず、演算ロジック部にもスピントロニクス技術を導入することを目指しています。この成果として、これまで、マイコンやFPGAや画像認識向けニューラルネットワーク型AIプロセッサの開発が始まっています。

ロジックについては、混載MRAMマクロ設計から、各種ロジックチップのパワーマネージメント(パワーゲーティングやクロックゲーティング等)アーキテクチャに加えて、論理設計・検証・物理設計までの一連の業務を行っています。

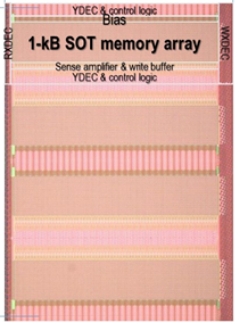

FPGA MPU

(IEEE ISSCC 2019)